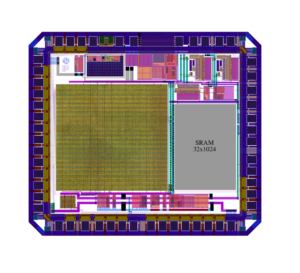

X-FAB Silicon Foundries together with crowd-sourcing IC platform partner Efabless Corporation announced the successful first-silicon availability of the Efabless RISC-V System on Chip (SoC) reference design. This open-source semiconductor project went from design start to tape-out in less than three months using the Efabless design flow based on open-source tools. The mixed-signal SoC, called Raven, […]

RISC-V

Hex Five adds MultiZone security to the AdaCore software ecosystem

Hex Five Security Inc., creator of MultiZone, the first trusted execution environment for RISC-V, today joined AdaCore’s Partner Program to enable the secure execution of Ada applications on RISC-V processors. As part of the initiative, Hex Five has developed an Ada version of the MultiZone SDK and published a reference application showing how to securely […]

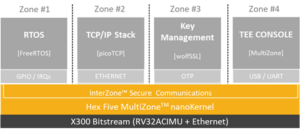

First secure IoT stack for RISC-V enables unlimited number of secure zones

wolfSSL and Hex Five Security, provider of MultiZone Security, the first Trusted Execution Environment for RISC-V, announce general availability of the industry-first secure IoT stack for RISC-V – a TLS 1.3 reference implementation of freeRTOS with hardware-enforced separation between OS, TCP/IP stack and root of trust. FreeRTOS is the leading real-time operating system in the market; […]

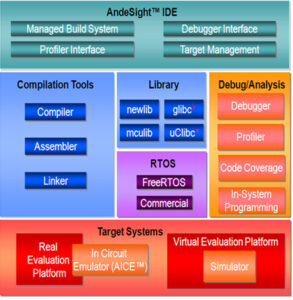

RISC-V IDE available for free download

Andes Technology Corporation, a founding member of the RISC-V Foundation announced the free download of its AndeSight Integrated Development Environment (IDE) to accelerate software development for RISC-V based SoC. AndeSight IDE is a professional IDE based on Eclipse with many useful Andes add-on features, developed and widely used over the past 13 years, which provides […]

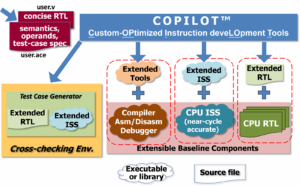

Design verification platform for RISC-V-based AI and ML semiconductor solutions

Valtrix Technologies, an EDA company delivering Design Verification (DV) solutions for the semiconductor industry, announced that Esperanto Technologies has selected Valtrix’s STING DV Platform for design verification of its energy-efficient semiconductor solutions for artificial intelligence (AI) and machine learning (ML) based on the open standard RISC-V instruction set architecture. Esperanto plans to use STING for verifying the […]

Framework enables pre-silicon software development with RISC-V

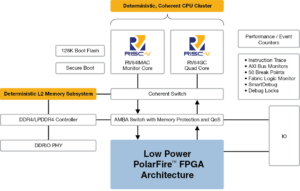

Antmicro has added support for the Linux-enabled PolarFire SoC revealed earlier by Microchip Technology in the open source Renode software development framework. Microchip PolarFire SoC is a new class of SoC FPGAs that combines the industry’s lowest power mid-range PolarFire FPGA family with a complete microprocessor subsystem based on the open, royalty-free RISC-V ISA. In a move […]

CPU cores with RISC-V technology now support the custom extension

Andes Technology announced its newly-released AndeStar V5 CPU cores – N25/N25F, NX25/NX25F, A25 and AX25 – support the Andes Custom Extension (ACE) feature. The AndeStar V5 architecture is the result of RISC-V technology incorporated with Andes innovations based on rich experience in serving embedded processor IPs for over 10 years. The ACE feature enables embedded […]

RISC-V SoftCPU contest winners announced

The RISC-V Foundation, a non-profit corporation controlled by its members to drive the adoption and implementation of the free and open RISC-V instruction set architecture (ISA), honored the winners of the RISC-V SoftCPU Contest for creating innovative FPGA based CPU implementations targeting the RISC-V ISA. The winners of the contest include: Charles Papon with VexRiscv in […]

SoC is based on royalty-free RISC-V instruction set architecture (ISA)

In a new era of computing driven by the convergence of 5G, machine learning and the internet of things (IoT), embedded developers need the richness of Linux-based operating systems. These must meet deterministic system requirements in ever lower power, thermally constrained design environments—all while addressing critical security and reliability requirements. Traditional system-on-chip (SoC) field programmable […]

RISC-V users to get performance boost with compiler, toolchain, and core combo

IAR Systems and Andes, the prominent CPU IP provider, announced that they have formed a partnership in order to deliver powerful development tools for Andes’ RISC-V-based solutions. IAR Systems provides the C/C++ compiler and debugger toolchain IAR Embedded Workbench. The toolchain offers leading code performance for size and speed, as well as extensive debug functionality […]